SDLS116 - DECEMBER 1983 - REVISED MARCH 1988

- Package Options Include Plastic and Ceramic DIPs and Ceramic Flat Packages

- Dependable Texas Instruments Quality and Reliability

#### description

These monolithic, edge-triggered J-K flip-flops feature gated inputs, direct clear and preset inputs, and complementary Q and  $\overline{Q}$  outputs. Input information is transferred to the outputs on the positive edge of the clock pulse.

Direct-coupled clock triggering occurs at a specific voltage level of the clock pulse, and after the clock input threshold voltage has been passed, the gated inputs are locked out.

These flip-flops are ideally suited for medium-to-highspeed applications and can result in a significant saving in system power dissipation and package count where input gating is required.

The SN5470 is characterized for operation over the full military temperature range of  $-55^{\circ}\text{C}$  to  $125^{\circ}\text{C}$ . The SN7470 is characterized for operation from  $0^{\circ}\text{C}$  to  $70^{\circ}\text{C}$ .

**FUNCTION TABLE**

| Ĺ   | IN  | OUT | PUTS |   |            |            |

|-----|-----|-----|------|---|------------|------------|

| PRE | CLR | CLK | J K  |   | a          | ā          |

| L   | Н   | L   | X    | X | Н          | L          |

| Н   | L   | L   | X    | × | L          | н          |

| L   | L   | ×   | X    | X | L†         | LT         |

| Н   | Н   | †   | L    | L | Φ0         | $\sigma_0$ |

| Н   | н   | Ť   | Н    | L | н          | L          |

| Н   | Н   | †   | L    | Н | L          | н          |

| Н   | Н   | t   | Н    | Н | TOGGLE     |            |

| Н   | Н   | L   | X    | X | $\sigma^0$ | σ₀         |

If inputs J and K are not used, they must be grounded. Preset or clear function can occur only when the clock input is low.

†This configuration is nonstable; that is, it will not persist when preset and clear inputs return to their inactive (high) level.

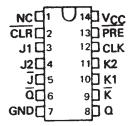

SN5470 . . . J PACKAGE SN7470 . . . N PACKAGE (TOP VIEW)

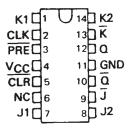

SN5470 ... W PACKAGE (TOP VIEW)

NC - No internal connection

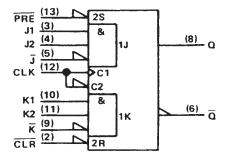

### logic symbol†

<sup>&</sup>lt;sup>†</sup>This symbol is in accordance with ANSI/IEEE Std. 91-1984 and IEC Publication 617-12.

Pin numbers shown are for J and N packages only.

#### positive logic

$$J = J1 \cdot J2 \cdot \overline{J}$$

$$K = K1 \cdot K2 \cdot \overline{K}$$

SDLS116 - DECEMBER 1983 - REVISED MARCH 1988

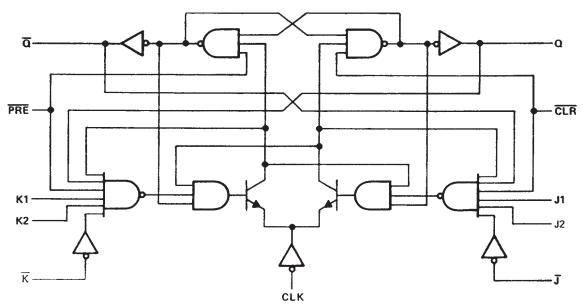

## logic diagram (positive logic)

**70-GATED J-K WITH CLEAR AND PRESET**

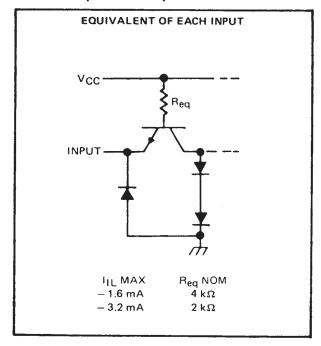

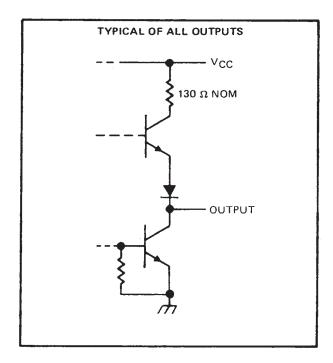

## schematics of input and outputs

## SN5470, SN7470 AND-GATED J-K POSITIVE-EDGE-TRIGGERED FLIP-FLOPS WITH PRESET AND CLEAR

SDLS116 - DECEMBER 1983 - REVISED MARCH 1988

#### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage, VCC (see Note 1)       |                 |

|----------------------------------------|-----------------|

| Input voltage                          |                 |

| Operating free-air temperature: SN5470 | – 55°C to 125°C |

| SN7470                                 | 0°C to 70°C     |

| Storage temperature range              | – 65°C to 150°C |

NOTE 1: All voltage values are with respect to network ground terminal.

#### recommended operating conditions

|                 |                                |                | SN5470      |     |       | SN7470 |         |       |      |

|-----------------|--------------------------------|----------------|-------------|-----|-------|--------|---------|-------|------|

|                 |                                |                | MIN         | NOM | MAX   | MIN    | NOM MAX |       | UNIT |

| Vcc             | Supply voltage                 |                | 4.5         | 5   | 5.5   | 4.75   | 5       | 5.25  | V    |

| $v_{iH}$        | High-level input voltage       |                | 2           |     |       | 2      |         |       | V    |

| VIL             | Low-level input voltage        |                |             |     | 8.0   |        |         | 8.0   | V    |

| ЮН              | High-level output current      |                |             |     | - 0.4 |        |         | - 0.4 | mA   |

| IOL             | Low-level output current       |                |             |     | 16    |        |         | 16    | mA   |

|                 |                                | CLK high       | 20          |     |       | 20     |         |       |      |

| $t_W$           | Pulse duration                 | CLK low        | 30          |     |       | 30     |         |       | ns   |

|                 |                                | PRE or CLR low | 25          |     |       | 25     |         |       |      |

| t <sub>su</sub> | Setup time before CLK †        |                | 20          |     |       | 20     |         |       | ns   |

| th              | Hold time-Data after CLK†      |                | 5           |     |       | 5      |         |       | ns   |

| $T_A$           | Operating free-air temperature |                | <b>– 55</b> |     | 125   | 0      | -       | 70    | °C   |

<sup>†‡</sup>The arrow indicates the edge of the clock pulse used for reference: †for the rising edge, ‡ for the falling edge.

## electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

| PARAMETER      |             | TEST CONDITIONS†                                   |                                                     | SN5470    |                  |       | SN7470 |      |       | T    |

|----------------|-------------|----------------------------------------------------|-----------------------------------------------------|-----------|------------------|-------|--------|------|-------|------|

|                |             |                                                    |                                                     | MIN       | TYP <sup>‡</sup> | MAX   | MIN    | TYP‡ | MAX   | UNIT |

| ViK            |             | V <sub>CC</sub> = MIN,                             | I <sub>I</sub> = - 12 mA                            |           |                  | - 1.5 |        |      | - 1.5 | V    |

| Vон            |             | V <sub>CC</sub> = MIN,<br>V <sub>IL</sub> = 0.8 V, | V <sub>1H</sub> = 2 V,<br>I <sub>OH</sub> = -0.4 mA | 2.4       | 3.4              |       | 2.4    | 3.4  |       | ٧    |

| VOL            |             | V <sub>CC</sub> = MIN,<br>V <sub>1L</sub> = 0.8 V, | V <sub>IH</sub> = 2 V,<br>I <sub>OL</sub> = 16 mA   |           | 0.2              | 0.4   |        | 0.2  | 0.4   | V    |

| I <sub>4</sub> |             | V <sub>CC</sub> = MAX,                             | V <sub>1</sub> = 5.5 V                              |           |                  | 1     |        |      | 1     | mA   |

|                | PRE or CLR  |                                                    | V 24V                                               |           |                  | 80    |        |      | 80    | μА   |

| ЧН             | All other   | V <sub>CC</sub> = MAX,                             | V <sub>1</sub> = 2.4 V                              |           |                  |       |        |      | 40    | ) "^ |

| PA             | PRE or CLR¶ |                                                    |                                                     |           |                  | - 3.2 |        |      | -3.2  |      |

| IL             | All other   | $V_{CC} = MAX$ , $V_{\uparrow} = 0.4 \text{ V}$    |                                                     | - 1.6 - 1 |                  |       | - 1.6  | m A  |       |      |

| loss           |             | V <sub>CC</sub> = MAX                              |                                                     | - 20      |                  | - 57  | - 18   |      | - 57  | mA   |

| Icc            |             | V <sub>CC</sub> = MAX,                             | See Note 2                                          |           | 13               | 26    |        | 13   | 26    | mA   |

<sup>&</sup>lt;sup>†</sup>For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions.

$<sup>^{\</sup>ddagger}$ All typical values are at V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25 °C.

<sup>§</sup>Not more than one output should be shorted at a time.

<sup>1</sup>Clear is tested with preset high and preset is tested with clear high.

NOTE 2: With all outputs open, ICC is measured with the Q and Q outputs high in turn. At the time of measurement, the clock input is at 4.5 V.

# SN5470, SN7470 AND-GATED J-K POSITIVE-EDGE-TRIGGERED FLIP-FLOPS WITH PRESET AND CLEAR

SDLS116 - DECEMBER 1983 - REVISED MARCH 1988

## switching characteristics, VCC = 5 V, TA = 25°C (see note 3)

| PARAMETER†       | FROM<br>(INPUT) | TO<br>(OUTPUT) | TEST CONDITIONS                    | MIN | ТҮР | MAX | UNIT |

|------------------|-----------------|----------------|------------------------------------|-----|-----|-----|------|

| f <sub>max</sub> |                 |                |                                    | 20  | 35  |     | MHz  |

| tPLH             | PRE or CLR      | Q or Q         |                                    |     |     | 50  | ns   |

| t <sub>PHL</sub> |                 |                | $R_L = 400 \Omega$ , $C_L = 15 pF$ |     |     | 50  | ns   |

| tPLH             | CLK             | Q or Q         |                                    |     | 27  | 50  | ns   |

| tPHL             |                 |                |                                    |     | 18  | 50  | ns   |

$<sup>^\</sup>dagger f_{max}$  = maximum clock frequency; tpLH = propagation delay time, low-to-high level output; tpHL = propagation delay time, high-to-low level output. NOTE 3: Load circuits and voltage waveforms are shown in Section 1.